# **Scale-Out Processors**

THÈSE Nº 5906 (2013)

PRÉSENTÉE LE 24 SEPTEMBRE 2013 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE D'ARCHITECTURE DE SYSTÈMES PARALLÈLES PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# Pejman LOTFI KAMRAN

acceptée sur proposition du jury:

Prof. W. Zwaenepoel, président du jury Prof. B. Falsafi, directeur de thèse Prof. G. De Micheli, rapporteur Dr P. Ranganathan, rapporteur Prof. P. Stenstrom, rapporteur

I am deathless, I am the eternal Lord For I have spread the seed of the Word. — Ferdowsi

To my parents...

# Acknowledgments

I dedicate this thesis to my parents. From the time that I can remember, they were the source of inspiration, motivation, and encouragement for me. Living far from them over the past five years has shown me the impact that they had on all of the success of my life. Thanks for all the trust, encouragement, and love!

I would like to thank my advisor, Prof. Babak Falsafi. He showed me the true meaning of academic research. Babak put me in an interesting and challenging research direction, which fulfilled all of my academic desires. If it were not for the joy of working on such an extraordinary research project, I would have left the Ph.D. program years ago when I faced, for the first time, the difficulties and pains of being a Ph.D. student. I also need to thank him for providing me with five years of financial support, which enabled me to focus on research.

I want to take this opportunity to thank the committee members of my thesis defense, Giovanni De Micheli, Partha Ranganathan, Per Stenstrom, and Willy Zwaenepoel. Their feedback and criticisms have improved this dissertation significantly.

My Ph.D. research was partially supported by EuroCloud, Project No 247779 of the European Commission 7th RTD Framework Programme – Information and Communication Technologies: Computing Systems. In addition to the financial support, as part of the EuroCloud project, I had the opportunity to work with wonderful colleagues from ARM, IMEC, Nokia, and University of Cyprus. In the last year of my Ph.D., I also benefited from an Intel Ph.D. fellowship award. I would like to thank the European Commission 7th RTD Framework Programme and Intel for partially supporting my Ph.D. research.

There are many people who contributed to this research; without them, I could never have achieved what I did. First and foremost, I need to thank Boris Grot. Since he joined PARSA (our laboratory) two years ago, my life as a Ph.D. student became easier. He is a great person to work with, and I was lucky to have him on my side. I want to acknowledge Mike Ferdman and thank him for being my role model in the first four years of my Ph.D. (when he was at PARSA). It is worthwhile to mention that I did send more emails to Mike than I sent to anybody else, and surprisingly, I always received a response quickly! Almutaz Adileh, Onur Kocberber, Djordje Jevdjic, Javier Picorel, and Stavros Volos are PARSA members who significantly contributed to the success of this thesis. Moreover, I need to mention EuroCloud members, Damien Hardy, Sachin Idgunji, Chrysostomos Nicopoulos, Emre Ozer, and Yanos Sazeides, who contributed

#### Acknowledgments

to this research. I also owe a debt of gratitude to Nikos Hardavellas, Tom Wenisch, Jason Zebchuk, and the many who contributed to the development of the Flexus infrastructure. Tom developed the core of the Flexus infrastructure, Jason coded the cache hierarchy, and Nikos built the analytic model that I used for most of my research work. Thank you all!

I am grateful to my friends and colleagues, Mohammad Alisafaee, Sotiria Fytraki, Effi Georgala, Cansu Kaynak, Jennifer Sartor, and Evangelos Vlachos, who listened to my talks, proofread my papers, and gave me invaluable feedback on various stages of my research. I also need to thank EuroCloud members, Bushra Ahsan, Tony Gore, Dragomir Milojevic, Andreas Panteli, Andreas Prodromou, and Isidoros Sideris, who accompanied me in various EuroCloud physical meetings, socialized after the meetings, and made physical meetings fun.

I would like to thank Nancy Chong, Ved Gund, Dongha Jung, Samira Manabi, Mehdi Modarressi, and Mahmood Naderan for all of the good times that I had when they were at EPFL. Specifically, the time when Dongha, Samira, and Mehdi were at EPFL was the best period of my Ph.D. life. I need to give special thanks to Hadi Esmaeilzadeh, my friend of 15 years, who was there for me every time I needed to talk to somebody. I also owe a debt of gratitude to Stéphanie Baillargues, Sylvie Fiaux, Valérie Locca, and Rodolphe Buret for handling the administrative tasks with which I needed help over the years.

There are many more who contributed to this success. If I wanted to mention every name, thousands of pages would not be enough. Please accept my apologies, and let me thank you all here. Thank you!

Lausanne, September 7, 2013

Pejman Lotfi-Kamran

# Abstract

Global-scale online services, such as Google's Web search and Facebook's social networking, run in large-scale datacenters. Due to their massive scale, these services are designed to scale out (or distribute) their respective loads and datasets across thousands of servers in datacenters. The growing demand for online services forced service providers to build networks of datacenters, which require an enormous capital outlay for infrastructure, hardware, and power consumption. Consequently, efficiency has become a major concern in the design and operation of such datacenters, with processor efficiency being of, utmost importance, due to the significant contribution of processors to the overall datacenter performance and cost.

Scale-out workloads, which are behind today's online services, serve independent requests, and have large instruction footprints and little data locality. As such, they benefit from processor designs that feature many cores and a modestly sized Last-Level Cache (LLC), a fast access path to the LLC, and high-bandwidth interfaces to memory. Existing server-class processors with large LLCs and a handful of aggressive out-of-order cores are inefficient in executing scale-out workloads. Moreover, the scaling trajectory for these processors leads to even lower efficiency in future technology nodes.

This thesis presents a family of throughput-optimal processors, called *Scale-Out Processors*, for the efficient execution of scale-out workloads. A unique feature of Scale-Out Processors is that they consist of multiple stand-alone modules, called pods, wherein each module is a server running an operating system and a full software stack. To design a throughput-optimal processor, we developed a methodology based on performance density, defined as throughput per unit area, to quantify how effectively an architecture uses the silicon real estate. The proposed methodology derives a performance-density optimal processor building block (i.e., pod), which tightly couples a number of cores to a small LLC via a fast interconnect. Scale-Out Processors simply consist of multiple pods with no inter-pod connectivity or coherence. Moreover, they deliver the highest throughput in today's technology and afford near-ideal scalability as process technology advances. We demonstrate that Scale-Out Processors improve datacenters' efficiency by 4.4x-7.1x over datacenters designed using existing server-class processors.

**Keywords:** Scale-Out Workloads, Datacenters, Efficient Processors, Performance Density, NOC-Out, Scale-Out Processors

# Résumé

A l'échelle mondiale, les services en lignes comme la recherche Web de Google et le réseau social Facebook, fonctionnent grâce à des centres de stockage de données de grande envergure. En raison de leur importance, ces services sont conçus pour redistribuer leur charge de travail et l'ensemble des données sur les milliers de serveurs des centres de stockage. La demande croissante des services en ligne a forcé les fournisseurs de services à construire des réseaux de données, qui nécessitent une énorme mise de fonds pour couvrir les frais liés à l'infrastructure, au matériel et à la consommation d'énergie. Par conséquent, l'efficacité est devenue une préoccupation majeure pour la conception et le fonctionnement de ces centres de stockage, et en particulier l'efficacité des processeurs, d'une extrême importance, en raison de leur contribution significative à l'augmentation des performances des centres de données et à la diminution des coûts d'exploitation.

Les applications à déploiement horizontal, qui sont à la base des services en ligne aujourd'hui, envoient des requêtes indépendantes, et ont de larges gammes d'instructions et peu de données locales. Par conséquent, elles bénéficient de conceptions de processeurs qui comportent de nombreux noyaux et un dernier niveau de cache (LLC) de taille modeste, une voie d'accès rapide à la LLC et des interfaces à large bande passante dans la mémoire. Les processeurs des serveurs existants, qui ont de grands LLC et quelques noyaux agressifs de type out-of-order sont inefficaces à l'exécution des applications à déploiement horizontal. Par ailleurs, la trajectoire de mise à l'échelle pour ces processeurs se traduit par une efficacité encore plus faible dans les futurs centres technologiques.

Cette thèse présente une famille de processeurs à performance optimale, appelés les *Processeurs Scale-Out*, pour l'exécution efficace de d'applications à déploiement horizontal. Une caractéristique unique des Processeurs Scale-Out est leur constitution en plusieurs modules autonomes, appelés pods. Chaque pod contient un serveur qui exécute un système d'exploitation et une pile logicielle complète. Pour concevoir un processeur à performance optimale, nous développons une méthodologie basée sur la densité de la performance (PD), qui est définie comme le débit par unité de surface, pour mesure comment une architecture efficace utilise la surface en silicium. La méthodologie proposée utilise un bloc de processeurs à performance optimale (c'est-à-dire un pod), qui associe étroitement plusieurs noyaux à un petit LLC via une interconnexion rapide. Les Processeurs Scale-Out sont simplement composés de plusieurs modules, sans connectivité ni cohérence. De plus, ils offrent les meilleures per-

### Résumé

formances technologiques actuelles et une évolutivité presque idéale avec les avancées de la technologie. Nous démontrons que les Processeurs Scale-Out améliorent l'efficacité des centres de stockage de données de 4.4 à 7.1 fois par rapport aux centres de données conçus pour utiliser des processeurs de classe serveur.

**Mots-clefs :** Applications à Déploiement Horizontal, Centre de Stockage des Données, Processeurs Efficaces, Densité de la Performance, NOC-Out, Processeurs Scale-Out

# Contents

| Dedication      |                                 |                                                 | iii  |  |

|-----------------|---------------------------------|-------------------------------------------------|------|--|

| Acknowledgments |                                 |                                                 | v    |  |

| Abs             | Abstract (English/Français) vii |                                                 |      |  |

| Con             | Contents xiii                   |                                                 |      |  |

| List            | List of figures xv              |                                                 |      |  |

| List            | of                              | tables                                          | xvii |  |

| 11              | [ntr                            | oduction                                        | 1    |  |

| ]               | 1.1                             | Why Not Existing Processors?                    | 3    |  |

| ]               | 1.2                             | Future Projections                              | 4    |  |

| ]               | 1.3                             | Scale-Out Design Methodology                    | 4    |  |

| ]               | 1.4                             | Organization of Scale-Out Processors            | 5    |  |

| ]               | 1.5                             | 3D Scale-Out Processors                         | 5    |  |

| ]               | 1.6                             | Dissertation Contributions                      | 6    |  |

| ]               | 1.7                             | Dissertation Organization                       | 7    |  |

| 2               | A Ca                            | ase For Scale-Out Processors                    | 9    |  |

| 2               | 2.1                             | What Do Scale-Out Workloads Want?               | 9    |  |

|                 |                                 | 2.1.1 Simple OoO Cores                          | 10   |  |

|                 |                                 | 2.1.2 Many Cores                                | 11   |  |

|                 |                                 | 2.1.3 Modestly Sized LLC                        | 11   |  |

|                 |                                 | 2.1.4 Fast Access to LLC                        | 12   |  |

|                 |                                 | 2.1.5 Minimal Connectivity                      | 13   |  |

|                 |                                 | 2.1.6 Adequate Number of Memory Interfaces      | 13   |  |

| 2               | 2.2                             | What Do Existing Processor Organizations Offer? | 14   |  |

|                 |                                 | 2.2.1 Conventional Processors                   | 14   |  |

|                 |                                 | 2.2.2 Tiled Processors                          | 15   |  |

|                 |                                 | 2.2.3 Optimized Tiled Processors                | 16   |  |

| 2               | 2.3                             | Metric for the Design-Space Evaluation          | 17   |  |

| 2               | 2.4                             | Methodology                                     | 17   |  |

|   |                                               | 2.4.1                                                                                                                                               | Design and Technology Parameters                                                                                                                                                                                                    | 17                                                                                                                                                                                             |

|---|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                               | 2.4.2                                                                                                                                               | Scale-Out Workloads                                                                                                                                                                                                                 | 18                                                                                                                                                                                             |

|   |                                               | 2.4.3                                                                                                                                               | Performance Evaluation                                                                                                                                                                                                              | 19                                                                                                                                                                                             |

|   | 2.5                                           | Results                                                                                                                                             | 5                                                                                                                                                                                                                                   | 19                                                                                                                                                                                             |

|   |                                               | 2.5.1                                                                                                                                               | 40nm Technology                                                                                                                                                                                                                     | 20                                                                                                                                                                                             |

|   |                                               | 2.5.2                                                                                                                                               | Projection to 20nm Technology                                                                                                                                                                                                       | 22                                                                                                                                                                                             |

|   |                                               | 2.5.3                                                                                                                                               | Summary                                                                                                                                                                                                                             | 23                                                                                                                                                                                             |

| 3 | AM                                            | ethodol                                                                                                                                             | logy to Design Scale-Out Processors                                                                                                                                                                                                 | 25                                                                                                                                                                                             |

|   | 3.1                                           |                                                                                                                                                     | tion                                                                                                                                                                                                                                | 26                                                                                                                                                                                             |

|   | 3.2                                           |                                                                                                                                                     | Out Design Methodology                                                                                                                                                                                                              | 26                                                                                                                                                                                             |

|   |                                               |                                                                                                                                                     | Pod as a Building Block                                                                                                                                                                                                             | 27                                                                                                                                                                                             |

|   |                                               |                                                                                                                                                     | Pod Features                                                                                                                                                                                                                        | 27                                                                                                                                                                                             |

|   |                                               |                                                                                                                                                     | Chip-Level Considerations                                                                                                                                                                                                           | 28                                                                                                                                                                                             |

|   | 3.3                                           |                                                                                                                                                     | dology                                                                                                                                                                                                                              | 29                                                                                                                                                                                             |

|   | 3.4                                           |                                                                                                                                                     | S                                                                                                                                                                                                                                   | 30                                                                                                                                                                                             |

|   |                                               | 3.4.1                                                                                                                                               | Model Validation                                                                                                                                                                                                                    | 30                                                                                                                                                                                             |

|   |                                               | 3.4.2                                                                                                                                               | Scale-Out Processors with Out-of-Order Cores                                                                                                                                                                                        | 31                                                                                                                                                                                             |

|   |                                               | 3.4.3                                                                                                                                               | Scale-Out Processors with In-Order Cores                                                                                                                                                                                            | 32                                                                                                                                                                                             |

|   |                                               | 3.4.4                                                                                                                                               | Projection to 20nm Technology                                                                                                                                                                                                       | 33                                                                                                                                                                                             |

|   |                                               |                                                                                                                                                     |                                                                                                                                                                                                                                     |                                                                                                                                                                                                |

|   |                                               | 3.4.5                                                                                                                                               | Summary                                                                                                                                                                                                                             | 34                                                                                                                                                                                             |

| 4 | Mic                                           |                                                                                                                                                     | Summary                                                                                                                                                                                                                             | 34<br><b>37</b>                                                                                                                                                                                |

| 4 | <b>Mic</b><br>4.1                             | roarchi                                                                                                                                             | •                                                                                                                                                                                                                                   |                                                                                                                                                                                                |

| 4 |                                               | <b>roarchi</b><br>Pods w                                                                                                                            | tecture of Scale-Out Processors                                                                                                                                                                                                     | 37                                                                                                                                                                                             |

| 4 | 4.1                                           | <b>roarchi</b><br>Pods w<br>Pods w                                                                                                                  | tecture of Scale-Out Processors vith Few Cores                                                                                                                                                                                      | <b>37</b><br>37                                                                                                                                                                                |

| 4 | 4.1                                           | <b>roarchi</b><br>Pods w<br>Pods w<br>4.2.1                                                                                                         | tecture of Scale-Out Processors         vith Few Cores         vith Many Cores                                                                                                                                                      | <b>37</b><br>37<br>38                                                                                                                                                                          |

| 4 | 4.1                                           | roarchi<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2                                                                                                       | tecture of Scale-Out Processors         vith Few Cores         vith Many Cores         Memory Traffic in Scale-Out Workloads                                                                                                        | <b>37</b><br>37<br>38<br>39                                                                                                                                                                    |

| 4 | 4.1<br>4.2                                    | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Metho                                                                                             | tecture of Scale-Out Processors         vith Few Cores         vith Many Cores         Memory Traffic in Scale-Out Workloads         NOC-Out                                                                                        | <b>37</b><br>37<br>38<br>39<br>41                                                                                                                                                              |

| 4 | 4.1<br>4.2                                    | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methoo<br>4.3.1                                                                                   | tecture of Scale-Out Processors         vith Few Cores         vith Many Cores         Memory Traffic in Scale-Out Workloads         NOC-Out         dology                                                                         | <ul> <li>37</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> </ul>                                                                                                             |

| 4 | 4.1<br>4.2                                    | roarchin<br>Pods w<br>4.2.1<br>4.2.2<br>Methoo<br>4.3.1<br>4.3.2                                                                                    | tecture of Scale-Out Processors         vith Few Cores         vith Many Cores         Memory Traffic in Scale-Out Workloads         NOC-Out         dology         Pod Parameters                                                  | <ul> <li>37</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>44</li> </ul>                                                                                                 |

| 4 | 4.1<br>4.2                                    | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methou<br>4.3.1<br>4.3.2<br>4.3.3                                                                 | tecture of Scale-Out Processors  vith Few Cores  vith Many Cores  Memory Traffic in Scale-Out Workloads  NOC-Out  NOC-Out  Pod Parameters  Technology Parameters                                                                    | <ul> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>44</li> <li>46</li> </ul>                                                                                                 |

| 4 | 4.1<br>4.2                                    | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methou<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                        | tecture of Scale-Out Processors vith Few Cores vith Many Cores Memory Traffic in Scale-Out Workloads NOC-Out NOC-Out Pod Parameters Technology Parameters Workloads                                                                 | <ul> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>44</li> <li>46</li> <li>47</li> </ul>                                                                                     |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methor<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Evalua                                              | tecture of Scale-Out Processors  ith Few Cores  ith Many Cores  Memory Traffic in Scale-Out Workloads  NOC-Out  NOC-Out  Pod Parameters  Technology Parameters  Workloads  Simulation Infrastructure                                | <ul> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>44</li> <li>46</li> <li>47</li> <li>47</li> </ul>                                                                         |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methou<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Evalua<br>4.4.1                                     | tecture of Scale-Out Processors  vith Few Cores  vith Many Cores  Memory Traffic in Scale-Out Workloads  NOC-Out  NOC-Out  Pod Parameters  Fechnology Parameters  Workloads  Simulation Infrastructure  tion                        | <ul> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>46</li> <li>47</li> <li>47</li> <li>47</li> </ul>                                                                         |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methou<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Evalua<br>4.4.1<br>4.4.2                            | tecture of Scale-Out Processors  ith Few Cores  ith Many Cores  Memory Traffic in Scale-Out Workloads  NOC-Out  NOC-Out  Out  Pod Parameters  Technology Parameters  Workloads  Simulation Infrastructure  tion  System Performance | <ul> <li>37</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>44</li> <li>46</li> <li>47</li> <li>47</li> <li>47</li> <li>48</li> </ul>                                     |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | roarchi<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methou<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Evalua<br>4.4.1<br>4.4.2<br>4.4.3                    | tecture of Scale-Out Processors<br>ith Few Cores                                                                                                                                                                                    | <ul> <li>37</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>46</li> <li>47</li> <li>47</li> <li>47</li> <li>48</li> <li>48</li> </ul>                                     |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methoo<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Evalua<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4          | tecture of Scale-Out Processors                                                                                                                                                                                                     | <ul> <li>37</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>44</li> <li>46</li> <li>47</li> <li>47</li> <li>47</li> <li>48</li> <li>49</li> </ul>                         |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | roarchin<br>Pods w<br>Pods w<br>4.2.1<br>4.2.2<br>Methoo<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Evalua<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5 | tecture of Scale-Out Processors<br>ith Few Cores                                                                                                                                                                                    | <ul> <li>37</li> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>44</li> <li>46</li> <li>47</li> <li>47</li> <li>47</li> <li>47</li> <li>48</li> <li>48</li> <li>49</li> <li>50</li> </ul> |

| 5  | Sca   | le-Out Processors with Large Dies                     | 53 |

|----|-------|-------------------------------------------------------|----|

|    | 5.1   | Motivation                                            | 53 |

|    | 5.2   | Methodology                                           | 54 |

|    |       | 5.2.1 TCO Model                                       | 54 |

|    |       | 5.2.2 Processor Price Estimation                      | 55 |

|    |       | 5.2.3 Experimental Setup                              | 56 |

|    | 5.3   | Evaluation                                            | 56 |

|    |       | 5.3.1 Performance and TCO                             | 56 |

|    |       | 5.3.2 Relative Efficiency                             | 58 |

|    |       | 5.3.3 Sensitivity to Processor Price                  | 60 |

| 6  | Sca   | le-Out Processors in the Post-Moore Era               | 61 |

|    | 6.1   | 3D Logic-on-Logic Technology                          | 62 |

|    | 6.2   | Why 3D Pods?                                          | 63 |

|    | 6.3   | Metric for the 3D Design-Space Evaluation             | 65 |

|    | 6.4   | 3D Pod Organization                                   | 65 |

|    | 6.5   | Methodology                                           | 66 |

|    |       | 6.5.1 Design and Technology Parameters                | 67 |

|    | 6.6   | Results                                               | 67 |

|    |       | 6.6.1 3D Scale-Out Processors with Out-of-Order Cores | 67 |

|    |       | 6.6.2 3D Scale-Out Processors with In-Order Cores     | 69 |

| 7  | Rela  | ated Work                                             | 73 |

|    | 7.1   | Scale-Out Design Methodology                          | 73 |

|    | 7.2   | NOC-Out: Microarchitecting a Scale-Out Processor      | 74 |

|    | 7.3   | Datacenter Analysis                                   | 75 |

|    | 7.4   | 3D Integration                                        | 75 |

| 8  |       | nclusions                                             | 77 |

|    | 8.1   | Limitations and Future Work                           | 79 |

| Bi | bliog | graphy                                                | 81 |

| Cı | ırric | ulum Vitae                                            | 91 |

# List of Figures

| 2.1 | Application instructions executed per cycle for an aggressive OoO core (out of maximum IPC of 4). | 10 |

|-----|---------------------------------------------------------------------------------------------------|----|

| 2.2 | Performance of 4-core workloads varying the LLC size.                                             | 11 |

| 2.3 | Per-core performance of 4-core workloads with a 4MB LLC varying the number                        |    |

|     | of cores (a) and chip-level performance with a 4MB LLC varying the number of                      |    |

|     | cores (b)                                                                                         | 12 |

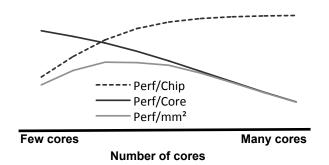

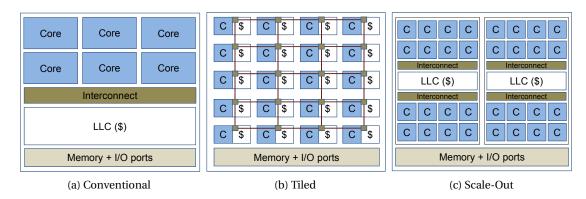

| 2.4 | A conventional processor.                                                                         | 14 |

| 2.5 | A tiled processor.                                                                                | 15 |

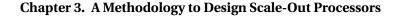

| 3.1 | Performance per core, performance per chip, and performance density for a                         |    |

|     | hypothetical workload.                                                                            | 26 |

| 3.2 | Comparison of conventional, tiled, and Scale-Out architectures. The Scale-Out                     |    |

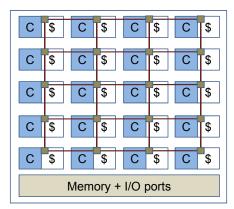

| 3.3 | design features two pods                                                                          | 28 |

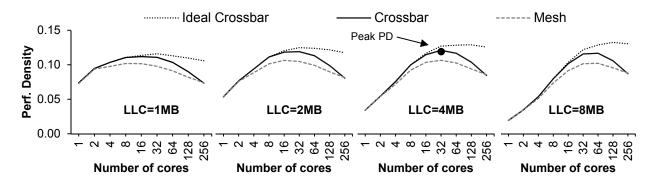

|     | cores and a 4MB LLC.                                                                              | 31 |

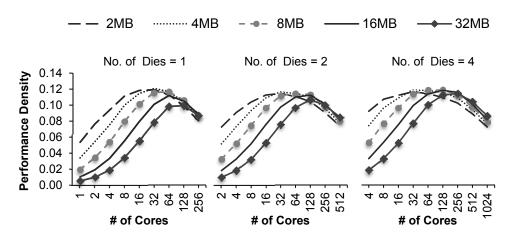

| 3.4 | Performance density for a system with out-of-order cores and a range of last-level                |    |

|     | cache sizes.                                                                                      | 31 |

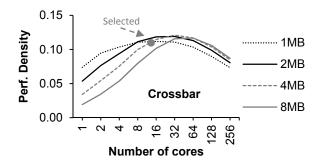

| 3.5 | Performance density of pods (OoO) based on a crossbar interconnect and various                    |    |

|     | LLC sizes.                                                                                        | 32 |

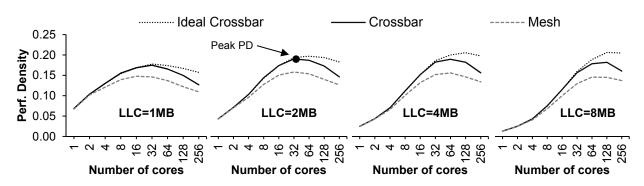

| 3.6 | Performance density for a system with in-order cores and a range of last-level                    |    |

|     | cache sizes.                                                                                      | 33 |

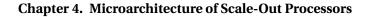

| 4.1 | Elements of tiled pods.                                                                           | 38 |

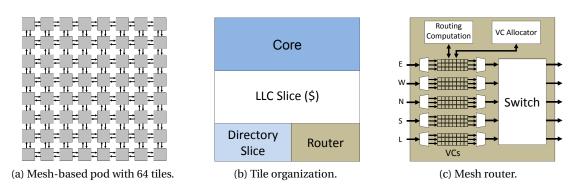

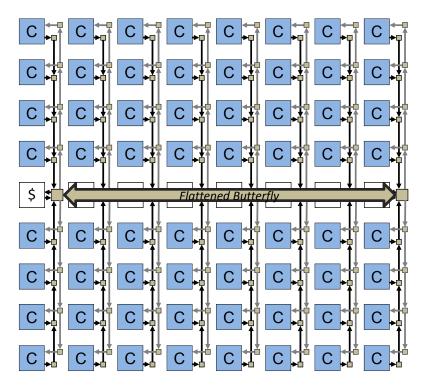

| 4.2 | Flattened butterfly topology (links from only one node shown for clarity)                         | 39 |

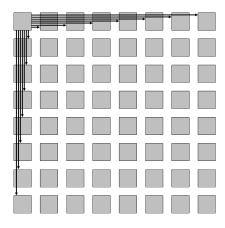

| 4.3 | Percentage of LLC accesses causing a snoop message to be sent to a core                           | 40 |

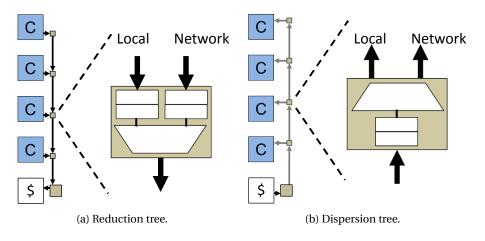

| 4.4 | NOC-Out organization.                                                                             | 41 |

| 4.5 | Details of NOC-Out networks.                                                                      | 42 |

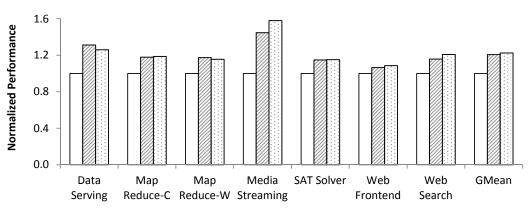

| 4.6 | System performance, normalized to a mesh-based design.                                            | 48 |

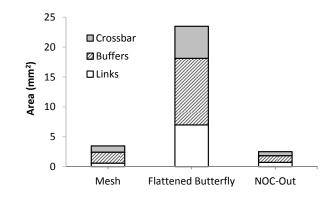

| 4.7 | NOC area breakdown.                                                                               | 49 |

| 4.8 | System performance, normalized to a mesh-based design, under a fixed NOC                          |    |

|     | area budget                                                                                       | 50 |

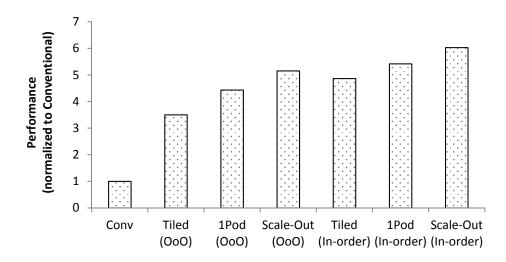

| 5.1 | Datacenter performance for various server processors normalized to a design                       |    |

|     | based on a conventional processor.                                                                | 57 |

### List of Figures

| 5.2 | Datacenter TCO for various server processors normalized to a design based on a conventional processor.                                                                                                                                         | 57       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

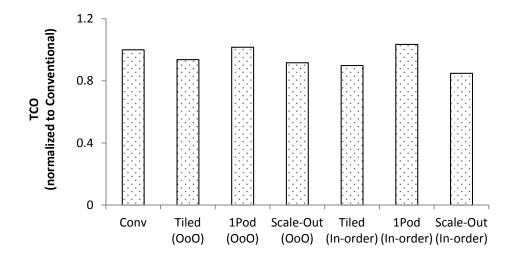

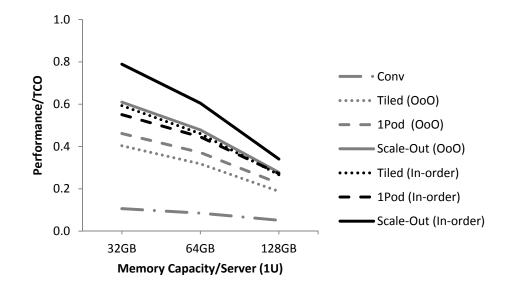

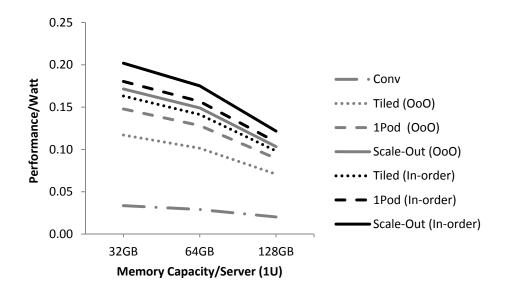

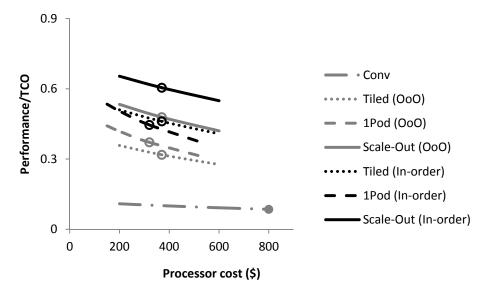

| 5.3 | Datacenter performance/TCO for different server chip designs. Data not nor-                                                                                                                                                                    | 50       |

| 5.4 | malized                                                                                                                                                                                                                                        | 59       |

| 5.5 | malized                                                                                                                                                                                                                                        | 59<br>60 |

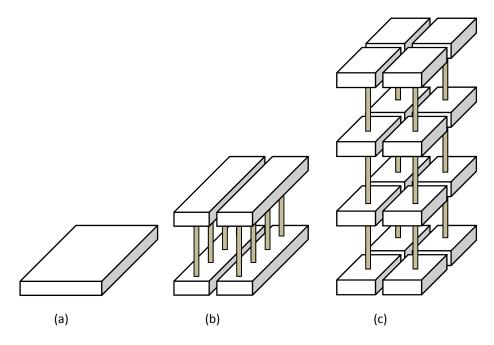

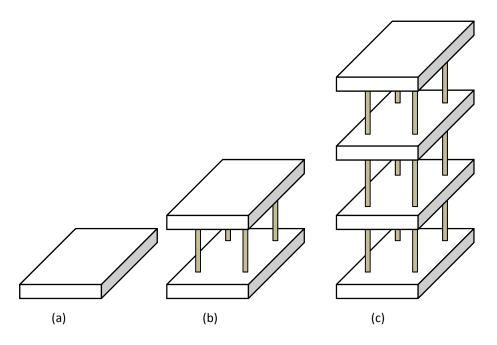

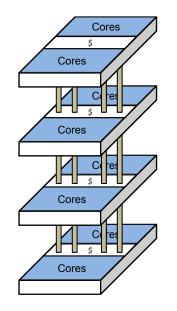

| 6.1 | Fixed-pod strategy with one logic die (a), two stacked logic dies (b), and four stacked logic dies (c). Every connected vertical piece is a pod (i.e., (a), (b), and (a) have one two and four node reconstructs)                              | 63       |

| 6.2 | (c) have one, two, and four pods, respectively)                                                                                                                                                                                                | 63<br>64 |

| 6.3 | Organization of a 3D pod.                                                                                                                                                                                                                      | 66       |

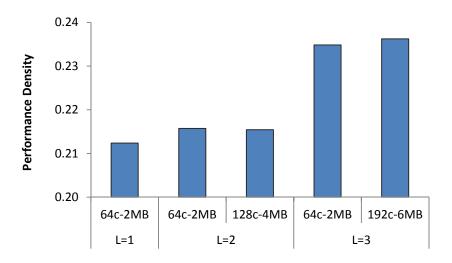

| 6.4 | Performance density for a system with out-of-order cores, a range of last-level                                                                                                                                                                |          |

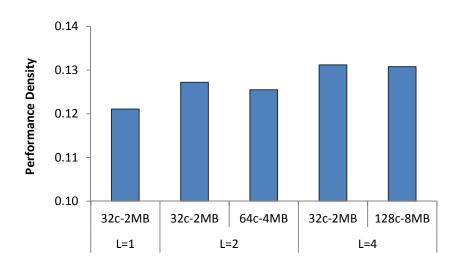

| 6.5 | cache sizes, and various numbers of stacked logic dies                                                                                                                                                                                         | 68       |

|     | is determined by the constraints.                                                                                                                                                                                                              | 69       |

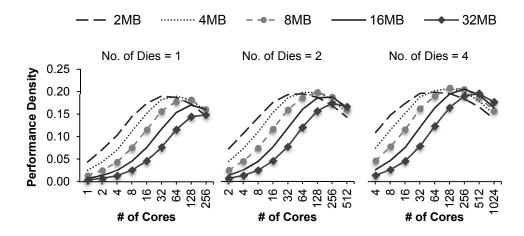

| 6.6 | Performance density for a system with in-order cores, a range of last-level cache sizes, and various numbers of stacked logic dies.                                                                                                            | 69       |

| 6.7 | Performance density of 3D Scale-Out Processors (in-order) with the fixed-pod<br>and the fixed-distance strategies. The labels on the x-axis show the configuration<br>of the pod and the number of stacked logic dies. The number of pods (not | 00       |

|     | shown) is determined by the constraints.                                                                                                                                                                                                       | 70       |

# List of Tables

| 2.1 | Area and power estimates for various system components at 40nm               | 18 |

|-----|------------------------------------------------------------------------------|----|

| 2.2 | Specification of various system components.                                  | 19 |

| 2.3 | Specification of various processor designs at 40nm                           | 20 |

| 2.4 | Specification of various processor designs at 20nm                           | 22 |

| 3.1 | System parameters for cycle-accurate, full-system simulations                | 29 |

| 3.2 | Performance density, area, power, and bandwidth requirements of various pro- |    |

|     | cessor designs                                                               | 34 |

| 4.1 | Evaluation parameters                                                        | 45 |

| 5.1 | Server chip characteristics.                                                 | 54 |

| 5.2 | TCO parameters.                                                              | 55 |

| 6.1 | Area and power estimates for various system components at 40nm               | 67 |

| 6.2 | Specification of various 2D and 3D Scale-Out Processors.                     | 71 |

# **1** Introduction

We are living in an era in which Information Technology (IT) is shaping our society. More than anytime in history, our society is dependent on IT for its day-to-day activities. Education, media, science, social networking, etc. are all affected by IT. The steady growth in processor performance is one of the driving forces behind the success and widespread adoption of IT.

Historically, the improvement in processor performance was driven by two phenomena: Moore's law [69] and Dennard scaling [28]. Technology scaling, which refers to the technology of shrinking transistor dimensions, provided processor designers with twice transistor density every two years (Moore's law). Moreover, the reduction in the supply voltage enabled processor designers to operate twice the number of transistors that technology offers without an increase in power consumption (Dennard scaling). Taking advantage of Moore's law and Dennard scaling, computer architects improved the processing power by constantly increasing the complexity of the processor pipeline and the frequency of the processor. Decades of technology scaling allowed powerful processors with deep and aggressive Out-of-Order (OoO) pipelines and high clock frequency to emerge.

Unfortunately, improving the performance of processors with the historical approach is no longer viable. As physical restrictions slow down the reduction of the supply voltage, Dennard scaling has effectively stopped [27]. While Moore's law is still valid and the number of transistors increases by a factor of two every two years, the failure of Dennard scaling makes power and energy the primary constraints of processors. As such, it is no longer desirable to increase the clock frequency of processors or increase the complexity of the processor pipeline to improve performance, as these approaches are not energy efficient [76]. For this reason, we did not see a noticeable increase in the clock frequency of processors for almost a decade.

As the historical approach for improving processor performance no longer works, since 2004, vendors have started to produce multi-core processors using relatively aggressive OoO cores [33]. This paradigm shift was motivated by the fact that many workloads have inherent thread-level parallelism and can benefit from multiple cores. With improvement in process technology, processor vendors keep the complexity of the cores constant and use the extra

transistors to increase the number of cores and the size of the last-level cache (LLC). As caches consume less energy compared to the cores, processors use almost half of their transistor budget for the LLC with the hope that a larger cache captures a larger fraction of the data working sets and results in faster execution.

In the meanwhile, we are witnessing that workloads are becoming more and more datacentric. We are living in the age of data explosion. The trend for many workloads, such as social networking or online advertising, is to collect and process larger and bigger volumes of data. Unfortunately, there is a mismatch between the workloads trend and the trend in the processor industry. While data-centric workloads are memory-intensive and do not benefit from aggressive OoO cores [40, 39, 30], such cores are offered in the existing products. Moreover, the little data locality in the emerging data-centric workloads makes large LLCs in the existing multi-core processors ineffective [43, 42, 39, 30]. To deliver the computational power necessary for future data-centric workloads, processors need to be redesigned to match the requirements of these workloads.

Global-scale online services represent an important class of data-centric workloads [30, 31]. As scalability is the primary concern for such services, they are designed to scale out (or distribute) the load across a large number of servers in datacenters. Service providers like Google, Microsoft, and Facebook rely on scale-out workloads that run in large-scale datacenters with thousands of servers to deliver media streaming, Web search, and social networking. The vast datasets of scale-out workloads are sharded across servers in datacenters. As data access latency is crucial, shards of the datasets are kept in large-capacity DRAM memories.

Scale-out workloads have common characteristics that can be leveraged to design highperformance processors, namely (a) massive parallelism; (b) little communication; (c) large instruction footprint; and (d) little data locality. As datacenters serve many independent requests coming from users across the world, scale-out workloads have abundant requestlevel parallelism. Due to the fact that these requests are mostly independent and the datasets are extremely large, there is rarely a need for communication when two requests are being processed. Moreover, these workloads serve a variety of complex requests, and as a result, their instruction footprints are large (hundreds of kilobytes to megabytes). Finally, the vast datasets combined with the independent nature of requests results in little data locality in these workloads.

A processor optimized for the execution of scale-out workloads needs to have many cores to benefit from the abundant parallelism in these workloads. Moreover, the little data locality calls for a medium-sized cache, which also leaves more die area for the cores. The large instruction footprints of scale-out workloads cannot be captured in an L1 instruction cache, and as such, they reside in the L2 cache. Due to the fact that instructions are shared across all the cores, the optimized processor needs to have a shared L2 cache that we refer to as the last-level cache (LLC). Moreover, because instructions are resident in the LLC, the optimized processor needs to provide a fast access path from the individual cores to the LLC for the

instruction delivery. The minimal communication in scale-out workloads calls for minimal connectivity between the cores and makes designing a fast access path from the cores to the LLC trivial. Finally, as the datasets are resident in memory, the optimized processor needs to have high-bandwidth interfaces to frequently access memory.

Scale-out workloads have multi-tier architecture with complex software stacks. Even though there is little communication in these workloads due to the independence of requests and the vast data working set sizes, the shared-memory programming model is valued in the scale-out domain, as it simplifies software development and facilitates the use of existing software stacks. This fact, combined with the common characteristics of scale-out workloads, calls for a shared-memory processor with many cores, a modestly sized LLC, minimal connectivity, fast access to the LLC, and high-bandwidth memory channels.

## 1.1 Why Not Existing Processors?

Today's volume servers are designed with processors that are essentially general-purpose. These conventional processors combine a handful of aggressively speculative and high clockfrequency cores supplemented by a large shared on-chip cache. As manufacturing technology provides higher transistor density, conventional processors use the additional transistors to scale up the core count, cache capacity, coherence mechanism, and interconnect.

Recently, tiled processors have emerged as competition to volume processors in the scale-out server space [90]. Recognizing the importance of per-server throughput, these processors use a large number of relatively simple cores, each with a slice of the shared LLC, interconnected via a packet-based mesh interconnect. Lower-complexity cores are more efficient than those in conventional designs [59]. Despite the differences in the chip-level organization, the technology scaling trends of tiled processors are similar to conventional designs; each technology generation affords more tiles, which increases the core count, cache capacity, and interconnect resources.

In the context of processors for scale-out workloads, both architectures make suboptimal use of the die area and cannot maximize throughput. One of the inefficiencies of these processors is their large last-level caches. Maximizing throughput necessitates a careful choice in the size of the cache. Smaller caches that can capture the dynamic instruction footprints of scaleout workloads afford more die area for the cores without penalizing per-core performance. Moreover, we demonstrate that while the simpler cores found in tiled designs are more effective than conventional server cores for scale-out workloads, the latency incurred by the on-chip interconnect in tiled organizations lowers performance and limits the benefits of integration, as additional tiles result in more network hops and longer delays.

### 1.2 Future Projections

As process technology advances and more transistors become available, existing processors use the higher transistor density to increase the number of cores and size of the last-level cache. While scale-out workloads do not benefit from a large last-level cache and existing processors already have large last-level caches beyond what is required for these workloads, future projections indicate that processor vendors plan to increase the size of the LLC even further. Consequently, not only existing processors suffer from large last-level caches when they execute scale-out workloads, but also, this problem exacerbates as manufacturing technology improves.

Moreover, scale-out workloads require fast access to the last-level cache at minimum because their instruction footprints are large; hence, they reside in the LLC. As technology scales and manufacturing capability increases, more cores will be added to processors. In existing processor organizations, there is a direct relationship between the access latency to the LLC and the number of cores that share it. As the number of cores in existing processor organizations increases, the access latency to the LLC also increases.

While existing processors suffer from large last-level caches and/or slow access to the LLC, the projections indicate that both shortcomings will exacerbate with improvement in transistor scaling. The shortcomings of existing processors for the execution of scale-out workloads necessitate a processor design methodology, which would eliminate the shortcomings and enable seamless scalability with improvement in transistor scaling.

### 1.3 Scale-Out Design Methodology

Scale-out datacenters require processors with many cores and a fast access path to the lastlevel cache to maximize throughput. As scale-out workloads do not benefit from a large last-level cache (due to little data locality in these workloads), processors optimized for scaleout workloads should dedicate most of their die area to cores and maximize the number of cores. While it is easy to increase the core count, we demonstrate that existing processor organizations fundamentally cannot fulfill both requirements – i.e., many cores and fast access from the cores to the LLC – simultaneously.

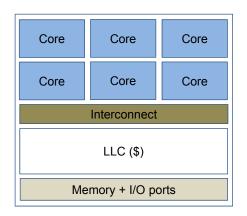

As more cores are added to a processor with a fixed-size LLC, both the die area of the processor and the physical distance between the individual cores and the last-level cache increase. Because the time it takes for a core to access the last-level cache is proportional to the physical distance between the core and the LLC, the longer distance between the core and the LLC, which is an artifact of integrating more cores, results in slower access to the LLC. Existing processor organizations are fundamentally incapable of providing fast access to the LLC while many cores are integrated in the processor. We need a new processor organization to break the relationship between core count and LLC access latency. The new processor organization should enable integrating many cores while providing low LLC access latency. To address the limitation of existing processor organizations, we propose the scale-out design methodology. The scale-out design methodology calls for many-core processors based on the notion of pods. A pod is a module that tightly couples several cores to a modestly sized LLC through a low-latency interconnect. The proposed methodology breaks the relationship between more cores and higher LLC access latency by partitioning the die area of a processor and integrating a pod in each partition. Each pod is a self-contained server-on-a-chip running a full software stack. We formulate a methodology to determine the optimal number of cores and LLC capacity to integrate in a pod for peak throughput. The proposed design, called the Scale-Out Processor, delivers peak throughput in today's process technology and affords near-ideal scalability as the technology scales.

### 1.4 Organization of Scale-Out Processors

As Scale-Out Processors are composed of many pods, the microarchitecture of pods is essentially the main factor that determines the performance of Scale-Out Processors. While partitioning the die area through integrating many pods enables Scale-Out Processors to break the relationship between core count and LLC access latency across pods, providing fast access from cores to the LLC within a pod is necessary for the success of Scale-Out Processors.

Unfortunately, the existing many-core organizations force a compromise between performance and area cost [64]. While mesh-based tile organizations have a modest area and wire cost, they incur latency overheads through a many-hop organization. In contrast, many-core organizations based on the richly connected topologies, such as a flattened butterfly [55], offer low LLC access latency at high area and wire cost. Pods in Scale-Out Processors require organizations that have low area overhead and provide fast access to the last-level cache.

To provide fast access to the LLC with low area overhead, we propose a novel organization using a simple and critical observation: there is almost no core-to-core communication in scale-out workloads [64, 71, 63]. Based on this observation, the proposed organization (a) decouples cores and the last-level cache; (b) eliminates all unneeded core-to-core links; and (c) uses specialized core-to-LLC networks to connect cores to the last-level cache and vice versa. The bottom line is that the proposed organization delivers the performance of the state-of-the-art with  $1/10^{th}$  of the area.

### 1.5 3D Scale-Out Processors

As scaling down transistor dimensions becomes more complicated and challenging [10], the validity of Moore's law, which is the primary driving force behind the growth of the semiconductor industry, is expected to end [66]. Three-dimensional integration of multiple logic dies is a propitious mechanism that can extend the validity of Moore's law. In a 3D integration, multiple logic dies are stacked on top of each other and interconnected by through-silicon vias (TSVs). In a conventional 2D integration, the scaling of transistor dimensions implies more transistors and also larger average distance between the transistors. As technology scales and more transistors become available, the average distance between the transistors increases because it is impossible to scale global wire length with technology [12]. On the contrary, in a 3D integration, more transistors become available by stacking more logic dies on top of each other. As the vertical distance is much shorter (i.e., in the order of  $\mu$ m) than the horizontal distance (i.e., in the order of mm), more transistors in a 3D integration come without an increase in the average distance.

Because of the negligible vertical distance in a 3D integration, as well as to benefit from the 3D integration, pods should span vertically across all of the logic dies that are stacked on top of each other. This feature enables two possible directions for 3D integrated pods: (1) Pods grow the number of cores and LLC capacity as more logic dies are added while benefiting from the 3D integration to keep the on-chip distance constant; and (2) Pods keep their core count and LLC capacity constant and use 3D integration to reduce the on-chip distance. Negligible vertical distance enables 3D pods to have either more cores and larger LLC or shorter on-chip distance as compared to 2D pods. Consequently, 3D integration increases the throughput of Scale-Out Processors.

# 1.6 Dissertation Contributions

In this dissertation, we investigate the design of throughput-optimal processors for scaleout workloads. We begin by demonstrating that existing processor organizations fall short of efficiency in executing scale-out workloads. We then motivate and justify Scale-Out Processors and provide an organization for them. We show that Scale-Out Processors can significantly increase performance per total cost of ownership in datacenters. We conclude by exploring the design space of Scale-Out Processors manufactured with 3D logic-on-logic technology as the likely enabler of Moore's law when transistor scaling stops.

Through a combination of analytic modeling, trace-driven analysis, and cycle-accurate, fullsystem simulation of various multi-core processors running scale-out workloads, we demonstrate:

**Inefficiency of existing processors.** We demonstrate that existing processors are incapable of running scale-out workloads efficiently. We identify misallocation of on-chip resources and long LLC access latency as the two main bottlenecks of existing processors.

**Fundamental limitation of existing processor organizations.** We identify the relationship between the increase in core count and the increase in LLC access latency as the fundamental limitation of existing processor organizations. This fundamental limitation prevents existing processor organizations from maximizing throughput of scale-out workloads.

Scale-Out Processors. We demonstrate the scale-out design methodology that enables avoid-

ing the fundamental limitation of existing processor organizations – namely, the relationship between the increase in core count and the increase in LLC access latency. Moreover, we demonstrate the effectiveness of the resulting processors, i.e., Scale-Out Processors, for efficient execution of scale-out workloads.

**Microarchitecture of Scale-Out Processors.** We show that existing multi-core microarchitectures are either area-inefficient or performance limiters in the context of Scale-Out Processors. Taking advantage of the characteristics of scale-out workloads, we demonstrate a novel microarchitecture for Scale-Out Processors to achieve both area efficiency and high performance.

**Benefits of Scale-Out Processors in datacenters.** We demonstrate the effectiveness of Scale-Out Processors in the context of datacenter efficiency. We use *Performance per Total Cost of Ownership* as the efficiency metric at datacenters to show the superiority of Scale-Out Processors as compared to existing processors.

**Multi-pod Scale-Out Processors.** We demonstrate that Scale-Out Processors with large dies are more efficient than Scale-Out Processors with small dies. We compare single- and multi-pod Scale-Out Processors at datacenters and show that multi-pod Scale-Out Processors are more efficient.

**Scale-Out Processors in the post-Moore era.** We study the impact of 3D logic-on-logic technology on Scale-Out Processors. Three-dimensional logic-on-logic technology is the likely successor of transistor scaling for extending the validity of Moore's law. We demonstrate that Scale-Out Processors can leverage features specific to 3D logic-on-logic technology to improve performance beyond what is possible in a standard 2D process.

### 1.7 Dissertation Organization

The rest of this dissertation is organized as follows. In Chapter 2, we study the behavior of scale-out workloads and demonstrate the mismatch between existing processor organizations and the requirements of these workloads. In Chapter 3, we introduce the scale-out design methodology and quantify its benefits. In Chapter 4, we microarchitect a Scale-Out Processor to minimize the area cost and maximize the performance. In Chapter 5, we compare various processor organizations in the context of datacenter total cost of ownership to show the effectiveness of multi-pod Scale-Out Processors. In Chapter 6, we extend the organization of Scale-Out Processors for implementation in 3D logic-on-logic technology as the likely enabler of the post-Moore era. Finally, we comment on related research in Chapter 7 and conclude in Chapter 8.

# **2** A Case For Scale-Out Processors

Datacenters are the computing platforms for delivering scalable online services. Google, Microsoft, and Facebook rely on networks of datacenters to deliver search capabilities, social networking, and a growing number of other offerings. The scale-out software architecture at the core of the online service model effectively accommodates dataset and demand growth by simply distributing the load on many servers, as servers handle independent requests that do not share any state.

With typical scale-out workloads distributed across thousands of servers inside a datacenter, performance characteristics of each server dictate the datacenter's throughput. In TCO-conscious datacenters, performance per TCO dollar is maximized by increasing the throughput of each server processor, which enables better memory utilization and affords higher perserver performance without a commensurate increase in cost [92].

To maximize the throughput of scale-out workloads, server processors need to have many cores to serve independent requests in parallel and also need to get high throughput from each individual core. For individual cores to deliver high throughput, server processors need to provide a fast path to the LLC that holds the instructions and data secondary working sets.

We motivate the need for Scale-Out Processors based on the observation that the two requirements (i.e., many cores and a fast path to the LLC) cannot be satisfied simultaneously with existing many-core processor organizations. In existing organizations, as the number of cores increases, the distance from the cores to the LLC increases, which results in longer LLC access latency. In this chapter, we show that existing processors are not capable of meeting the two requirements at the same time and, as such, are not suitable for the execution of scale-out workloads.

### 2.1 What Do Scale-Out Workloads Want?

In this section, we examine a representative set of scale-out workloads in order to understand the demands they place on server processors. Research analyzing the scale-out workload

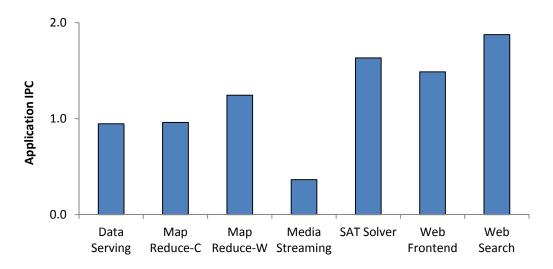

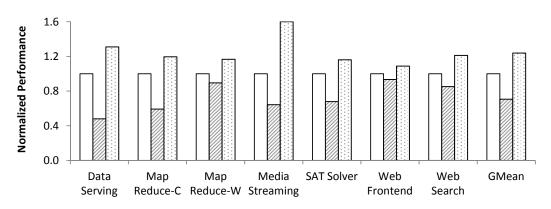

Figure 2.1: Application instructions executed per cycle for an aggressive OoO core (out of maximum IPC of 4).

domain has shown that a key set of traits holds across a wide range of workloads, including Web search, media streaming, and Web serving. These traits can be summarized as request independence, little communication, large instruction footprint, and vast dataset [30]. These traits favor server processors with (a) many simple OoO cores; (b) modestly sized LLC; (c) a fast access path to the LLC; (d) minimal connectivity between cores; and (e) high-bandwidth memory interfaces. Next, we examine each of these requirements in more detail.

#### 2.1.1 Simple OoO Cores

Scale-out workloads have vast datasets that are kept in memory to minimize the response latency [30]. On one hand, scale-out workloads are memory-intensive and spend most of their time accessing data in memory; as such, their benefit from aggressive OoO cores is limited [30]. On the other hand, the instruction-level parallelism (ILP) in these workloads is not as low as conventional memory-intensive workloads (e.g., database workloads) [79].

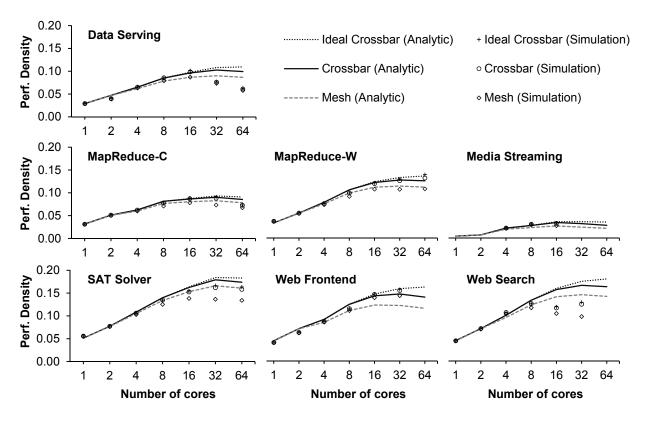

Figure 2.1 shows the application instructions per cycle (IPC) for an aggressive OoO core with commit width of four and 2GHz frequency. Out of seven scale-out workloads, only one of them (i.e., Media Streaming) has an IPC of less than one. Two of the workloads (i.e., Data Serving and MapReduce-C) have an IPC of around one, and four of the workloads have an IPC of greater than one and less than two. While the core is aggressive OoO and can commit up to four instructions per cycle, on average, at most two instructions are committed every cycle. These results corroborate prior work [30] and show that aggressive OoO cores are not suitable for scale-out workloads. Moreover, four out of seven workloads have an IPC of greater than one, which suggests that simple OoO cores can be useful for these workloads, corroborating prior work [79].

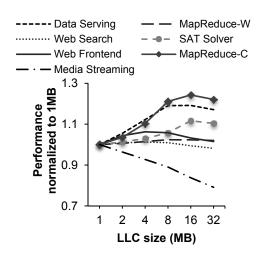

Figure 2.2: Performance of 4-core workloads varying the LLC size.

#### 2.1.2 Many Cores

As mentioned in the previous section, scale-out workloads are memory-intensive and spend a considerable fraction of their execution time waiting for data to arrive from memory. As such, aggressive OoO cores are not well-suited for the execution of these workloads. Fortunately, scale-out workloads, like media streaming, social networking, or Web search, handle a stream of requests that are, to an overwhelming extent, mutually independent [30]. Fundamentally, request independence is the feature that makes scale-out workloads inherently parallel. The abundant request-level parallelism argues for processor designs with a large number of cores to maximize throughput.

#### 2.1.3 Modestly Sized LLC

We seek to establish the range of last-level cache sizes appropriate for scale-out workloads. As it has been shown that a Non-Uniform Cache Architecture (NUCA) L2 cache matches the performance of a multi-level cache hierarchy [53], we evaluate a two-level cache hierarchy with a NUCA LLC in this dissertation.

We analyze the cache requirements of scale-out workloads by sweeping the size of the LLC from 1 to 32MB. The results are presented for a quad-core processor, but note that the general trends are independent of the core count. Details of the methodology can be found in Section 2.4.3.

Figure 2.2 plots the performance (i.e., the aggregate number of application instructions committed per cycle [89]) of individual applications normalized to a design with a 1MB LLC. For most of the workloads, LLC capacities of 2-8MB are sufficient to capture the instruction footprint and secondary working set. Beyond this range, larger cache configurations provide limited benefit because the enormous data working sets of the workloads exhibit little reuse in the LLC. Two of the workloads (MapReduce-C and SAT Solver) exhibit a different behavior,

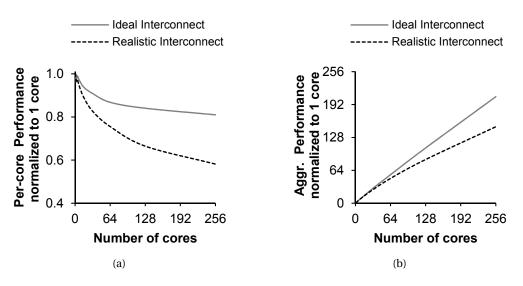

Figure 2.3: Per-core performance of 4-core workloads with a 4MB LLC varying the number of cores (a) and chip-level performance with a 4MB LLC varying the number of cores (b).

as larger caches do help in capturing the secondary working set. However, even for these workloads, a 16-fold increase in cache size from 1 to 16MB translates into a performance gain of just 12-24%. Cache capacity beyond 16MB is strictly detrimental to performance, as the reduction in miss rate is offset by the increased access latency. These results corroborate prior characterizations of scale-out and traditional server workloads executing on chip multiprocessors [30, 43].

#### 2.1.4 Fast Access to LLC

We analyze the sensitivity of scale-out workloads to the on-chip distance and the sharing degree. We fix the LLC size at 4MB and examine the performance as the number of cores varies from 1 to 256. Figure 2.3 plots per-core performance (a) and throughput per chip (b) averaged across workloads and normalized to a single-core baseline. The two lines in the figures correspond to an ideal organization with a fixed-latency interconnect between each core and the LLC (solid gray line), as well as a realistic mesh-based interconnect where the physical distance between cores and cache banks affects the LLC access latency (dashed black line).

In the case of an ideal interconnect, Figure 2.3a shows that the degradation in per-core performance associated with having many cores share the LLC is small (e.g., 16% for a 128x increase in core count from 2 to 256 cores). As a result, Figure 2.3b demonstrates that aggregate performance can be improved by a factor of 210 by sharing a 4MB LLC among 256 cores.

In the case of a design subject to physical constraints, in which the distance to the LLC

grows with core count, the negative slope of the performance curve in Figure 2.3a is much steeper. The distance to the LLC has a direct effect on performance due to a combination of primary working set sizes greatly exceeding the L1 capacity and the memory-intensive nature of scale-out workloads, which makes these workloads particularly sensitive to the average memory access time. As a result, Figure 2.3b shows that a design based on a realistic interconnect reduces performance by 28% when compared to an ideal network at 256 cores, demonstrating how distance effects threaten the ability of server processors to reach their throughput potential.

Overall, scale-out workloads show limited benefit from LLC capacities beyond 8MB. Furthermore, a moderately sized cache can be effectively shared among a large number of cores. However, maximizing the performance in a system with a heavily shared LLC requires mitigating interconnect delays.

### 2.1.5 Minimal Connectivity